# Product Document

# **CMOSIS / AWAIBA**

is now

# Member of the ams Group

The technical content of this CMOSIS / AWAIBA document is still valid.

#### **Contact information:**

#### **Headquarters:**

ams AG

Tobelbaderstrasse 30

8141 Premstaetten, Austria

Tel: +43 (0) 3136 500 0

e-Mail: ams\_sales@ams.com

## 2.2 & 4.2 Megapixel machine vision CMOS image sensors

# **Evaluation System Manual**

#### **Change record**

| Issue | Date       | Modification                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 20/11/2009 | Origination                                                                                                                            |

| 2     | 2/3/2010   | Added test system description details                                                                                                  |

| 3     | 11/05/2012 | Changed info and pictures for updated board and software                                                                               |

| 4     | 17/01/2013 | Update to reflect the changes of the new software compatible with v2 and v3 sensors                                                    |

| 5     | 31/10/2013 | Updated description and screenshots to reflect latest demo software version Added startup procedure Removed "confidential" from footer |

### **Table of Contents**

| 1                         | Svst | em des             | scription     |                              |    |  |  |  |  |  |

|---------------------------|------|--------------------|---------------|------------------------------|----|--|--|--|--|--|

|                           | •    |                    | •             |                              |    |  |  |  |  |  |

|                           |      |                    |               |                              |    |  |  |  |  |  |

|                           | 1.2  | Block              | diagram       |                              | 4  |  |  |  |  |  |

|                           | 1.3  | 4                  |               |                              |    |  |  |  |  |  |

|                           | 1.4  | CMV2               | .000/400      | 0 board                      | 5  |  |  |  |  |  |

|                           |      | 1.4.1              | Casing        |                              | 5  |  |  |  |  |  |

|                           |      | 1.4.2              | Lens hole     | der                          | 5  |  |  |  |  |  |

|                           |      | 1.4.3              | Sensor +      | power and biasing            | 5  |  |  |  |  |  |

| 1.5 FPGA                  |      |                    |               |                              |    |  |  |  |  |  |

|                           | 1.6  | Came               | raLink Int    | terface                      | 7  |  |  |  |  |  |

|                           |      |                    |               | ed                           |    |  |  |  |  |  |

| 2                         | Fran | ne grab            | abber and PC8 |                              |    |  |  |  |  |  |

| _                         |      |                    |               |                              | _  |  |  |  |  |  |

| 3                         | Inst | alling t           | he syster     | n                            | 9  |  |  |  |  |  |

| 4                         | Run  | nning the system1  |               |                              |    |  |  |  |  |  |

| 4.1 Starting the software |      |                    |               |                              |    |  |  |  |  |  |

|                           | 4.2  | Softw              | are over\     | view                         | 10 |  |  |  |  |  |

|                           | 4.3  | 3 Software details |               |                              |    |  |  |  |  |  |

|                           |      | 4.3.1              | Control a     | area                         | 11 |  |  |  |  |  |

|                           |      | 4.3.2              | Register      | settings area                | 13 |  |  |  |  |  |

|                           |      |                    | 4.3.2.1       | Sensor registers             | 13 |  |  |  |  |  |

|                           |      |                    | 4.3.2.2       | FPGA registers               | 15 |  |  |  |  |  |

|                           |      | 4.3.3              | Image ar      | rea                          | 16 |  |  |  |  |  |

|                           |      | 4.3.4              | Image st      | atistics area                | 17 |  |  |  |  |  |

|                           |      |                    | 4.3.4.1       | Image statistics in ROI mode | 18 |  |  |  |  |  |

|                           |      | 4 2 E              | DEBLIG T      | rad.                         | 20 |  |  |  |  |  |

#### 1 SYSTEM DESCRIPTION

#### 1.1 OVERVIEW

The purpose of this document is to give an overview of the test system which for the 2/4Mpxl machine vision image sensors produced by CMOSIS. This test system can be used for testing and verifying the operation of the CMV2000/4000 image sensor.

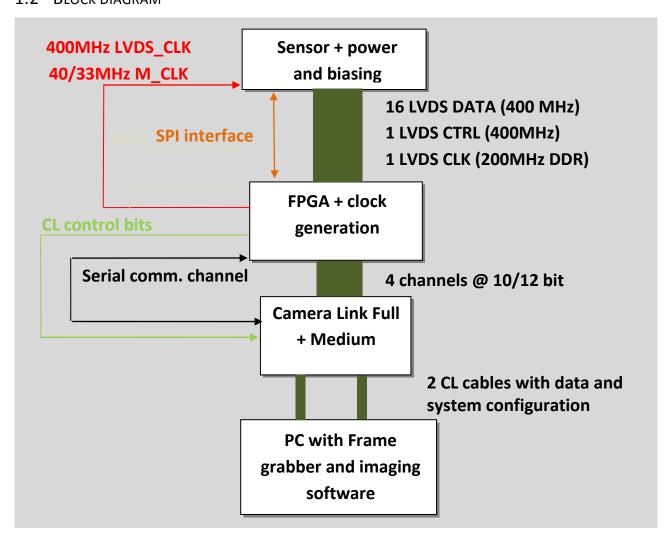

#### 1.2 BLOCK DIAGRAM

The block diagram above displays the different parts of the CMV2000/4000 test system. The three upper blocks are implemented on one PCB.

The fourth block is a standard third party frame grabber card which plugs into a PC's PCI Express bus (NI 1433). For this frame grabber and the PCB dedicated software has been developed in a LabVIEW environment.

#### 1.3 Contents of the test system

The following components should be present when the CMV2000/4000 test system is delivered.

- CMV2000/4000 board with lens holder

- Black metal casing with tripod holder

- 2 CameraLink cables (2m)

- NI PCI1433 frame grabber card (inside PC)

- Lenovo ThinkCentre mini tower model + custom software

- CD with documentation and software

#### 1.4 CMV2000/4000 BOARD

#### 1.4.1 **CASING**

The board is placed in a black metal box with the banana plug power cords, the CameraLink connectors and a tripod holder coming out at the side.

#### 1.4.2 LENS HOLDER

The CMV2000/4000 PCB is equipped with a C-mount lens holder. On this lens holder, off-the-shelf C-mount lenses can be fitted. The image sensor requires 2/3 (CMV2000) or 1 inch (CMV4000) or bigger C-mount lenses.

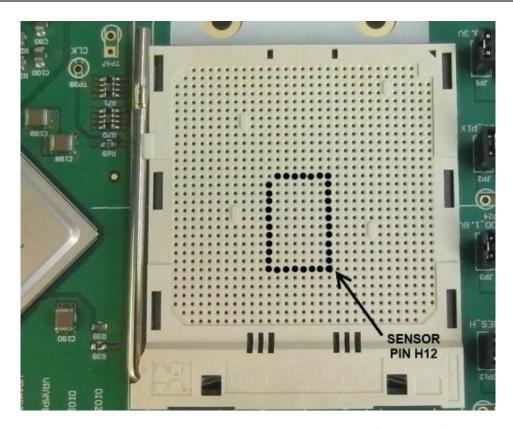

#### 1.4.3 Sensor + power and biasing

This part of the test board includes the sensor, its power sources and biasing (decoupling to ground). The sensor is easily removable from the test board because of the ZIF (zero insertion force) socket. If you want the replace the sensor, simply lift the metal handle upwards 90°; this will open the socket. Remove the sensor and place another back in the correct pins. No force is needed to place the sensor in the socket. Now close the socket by pushing the handle down until it 'clicks'. The sensor is now tightened and cannot fall out. The sensor should be placed according to the picture below:

All supplies are set to a correct value, but are adjustable using variable resistors if necessary (Do not exceed datasheet limits!). The power supply cables are connected as in the picture below:

#### 1.5 FPGA

The FPGA has 6 important roles in the test system:

- 1. Accept the LVDS data from the sensor (16 data channels @ 400Mbit/s, 1 LVDS clock channel @ 200MHz and 1 control channel @ 400Mbit/s)

- 2. Do bit and word alignment on the LVDS data

- 3. Generate the necessary driving signals for the sensor (clocks, I/O's, ...)

- 4. Generate the clocks needed by the sensor and CameraLink interface

- 5. Communicate with the sensor over the SPI interface

- 6. Communicate with the PC over the serial interface of the CameraLink

- 7. Prepare the data for the CameraLink interface

- 8. Send the data to the CameraLink interface together with the control bits and clocks

Taking the requirements above into account, we have chosen Xilinx Virtex4 FPGA for our test system. All functionality described in the requirements above is programmed into the FPGA. Communication between the PC and FPGA is possible using the serial channel of the CameraLink interface.

#### 1.6 CAMERALINK INTERFACE

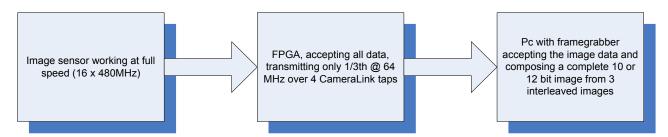

The interface between the test board (camera) and the PC uses the CameraLink standard. This standard is supported by many frame grabber cards on which the raw image data will be dumped. The test board is able to grab images at 400Mbps. This means that 10 and 12 bit images are grabbed by the system at 400MHz per LVDS channel.

Because of the limitations of the frame grabber, only 4 channels can be transferred from the sensor to the frame grabber and thus the software. In the software, you have the options to have a full resolution image (2048X\*2048H or 2048W\*1088H) but with the sensor running at 4 channel output mode. Or you can run the sensor at full speed, 16 channels output mode, but only four of those channels will be visible. Thus only 1/4<sup>th</sup> of the total resolution will be visible (512W\*2048H or 512\*1088H). In the software you have the choice of which outputs to use (0-3, 4-7, 8-11 or 12-15).

#### 1.6.1 LOW SPEED

In this mode, a partial image transfer is performed. Each pixel will consist of 10 or 12 bit data. The 4 taps (12 bit per tap) of the medium Camera Link will be running at 42 MHz to send 1/4th of the image to the PC. The sensor will run at full speed (400MHz/channel) but only 1/4th of the image data is transferred to the PC. This means that 4 images are needed to compose a full frame. This means that the frame rate at which movies or snapshots can be made will drop with a factor 4

$\rightarrow$  280 fps / 4 = 70 fps transferred to the PC.

For testing of the image sensor, this reduced frame rate will not pose any problems.

#### 2 FRAME GRABBER AND PC

A frame grabber card which can accept the Medium and Full CameraLink interface was chosen to complete the test system interface. The NI PCIe-1433 allows raw image data to be dumped at 4.8Gbit/s on the PC. This card is fitted in a PCI Express slot of the test system PC and uses two dedicated cables to connect to the CMV2000/4000 board.

The PCIe- 1433 frame grabber card comes with an API, which can easily be used in LabVIEW. This API is used to communicate with the frame grabber card and read the image from memory to display it on the screen.

See <a href="http://www.ni.com/pdf/manuals/372015a.pdf">http://www.ni.com/pdf/manuals/372015a.pdf</a> for more details on the PCle 1433 frame grabber card.

The PC in which the frame grabber card is inserted and on which the software is running has the following minimum requirements:

- Intel Core i3

- 2 GB DDR memory

- 500GB SATA hard disk

- Intel HD Graphics

- 16x DVD-ROM

- PCI-Express slots

On this PC, the LabVIEW RunTime Engine and the Vision Development Module will be installed. A dedicated CMV2000/4000.vi executable is written to grab and save images from the camera board. A detailed description of the software can be found in the next section.

#### 3 Installing the system

When installing the system, the following connections have to be made:

- 1. Connect the PC to its peripherals (keyboard, mouse and monitor)

- 2. Connect the PCB to a power supply (+5V/500mA, +9V/500mA, GND). (Note: make sure the two supplies have a common ground).

- 3. Connect the PCB to the PC via the two camera link cables. Use either cable to connect the camera link connector on the PCB labeled 'base' to the PC camera link port labeled 'base'. Use the other cable (medium) to connect PCB port 'medium' to the other frame grabber port on the PC. Next two figures show these connections.

#### Note:

The FPGA configuration is stored in an EPROM on the PCB. The FPGA is configured automatically when the power is switched on. On the PCB, there is a push button (labeled reset) that can be used to manually reconfigure the FPGA (resets the FPGA and initialize configuration when pressed)

#### 4 RUNNING THE SYSTEM

#### 4.1 STARTING THE SOFTWARE

Switch on the power supplies before starting the software. The current on the 5V and 9V should be around 300mA after initialization. If the 9V shows a current of about 60mA, the sensor isn't powered. This usually means that there is a bad contact with the ZIF socket. Reseat the sensor as in 1.4.3.

Log on to the PC using the 'demo user' account. No password is needed.

On the Desktop, there is a link to the demo software executable, called "Demo Software – CMV2000-4000 v3.exe". Double clicking this shortcut will launch the demo software.

When the software is started, the following actions have to be completed to read out images from the sensor:

- 1. The desired bit mode should be selected with the drop down menu under Image Mode.

- 2. The configuration file that corresponds with the sensor model and bit mode should be loaded with the LOAD CONFIG button and can be found on the provided CD.

- 3. Use the INITIALIZE button to upload the settings to the sensor

- 4. Now, the sensor is ready for operation, and images can be read out with the GRAB SINGLE or GRAB CONTINUOUS button

GRAB SINGLE will send one request to the sensor for the desired amount of frames, while the GRAB CONTINUOUS button will read-out frames continuously at the maximum possible frame rate.

#### 4.2 SOFTWARE OVERVIEW

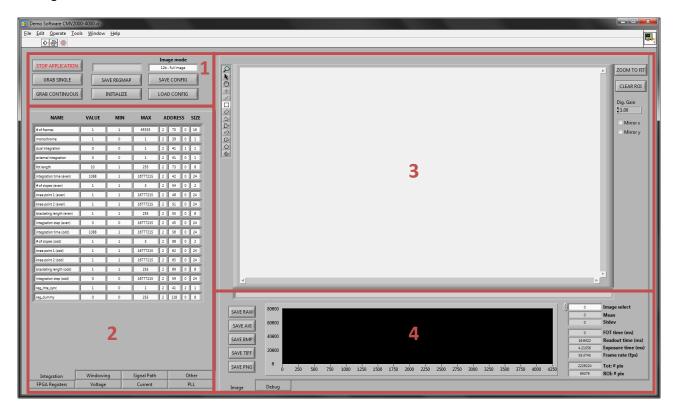

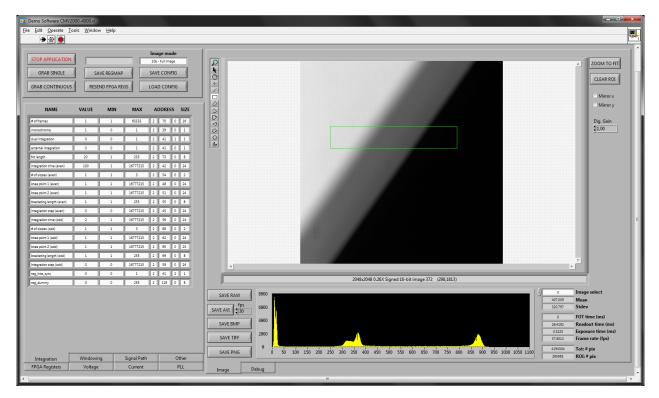

Next figure shows a screenshot of the demo software.

The four main areas of the software are:

- 1. **Control area:** The user can control the software (grab frames, save and load configuration files ...) via a number of push buttons.

- 2. **Register settings area:** The user can set the registers of the sensor. The registers are grouped into a number of tabs for better readability.

- 3. Image area: The images acquired from the sensor are displayed in this image viewing plane.

- 4. **Image statistics area:** A number of image and software statistics are displayed here.

#### 4.3 SOFTWARE DETAILS

#### 4.3.1 CONTROL AREA

The 9 controls in the Control Area are:

- 1. **STOP APPLICATION** button: Click this button to stop the application from running and exit to the labview runtime environment. Then the window can be closed. It is required to use this button to stop the program, instead of closing the window while it is still running.

- 2. **GRAB SINGLE** button: Click this button to grab a single sequence of frames. The number of frames in the sequence is set in the 'register settings area'. When the single grab has finished, the 'image 'area' will be updated.

- 3. **GRAB CONTINUOUS** button: This button has the same function as the 'grab single' button. The difference is that this button has a different latching action. By clicking it once, it will be enabled. As long as it is enabled, the software will continuously request sequences of frames and update the image area. This mode is also called 'video mode'. To stop the video mode, click the 'grab continuous button' again. This will reset the button to its disabled state.

- 4. **SAVE REGMAP** button: Click this button to save a register map to a text file. The register map that is saved is a 4-by-128 array of 8-bit values representing the register settings that are currently set in the 'register settings area'. The third row of the 4-by-128 map is the register map of the sensor. The other three rows are registers to control the FPGA.

- 5. **INITIALIZE** button: The settings from the 'register settings area' are uploaded to the FPGA and sensor incrementally. This means that a value is transferred only when it is changed by the user in the software. The 'reload FPGA button' will force a complete transfer of all settings from software to the FPGA. This allows the user to fully reconfigure the FPGA registers if needed (for example after an FPGA reset). During normal operation, this button is not needed.

- 6. **SAVE CONFIG** button: By clicking this button, a configuration file can be saved. A configuration file is a human-readable version of the sensor register map. The saved text file has the same information as the register map that is saved using the 'save regmap button'. The advantage of a configuration file is that it can be reloaded into the software using the 'load config button'. (Tip: save the configuration files with a .txt extension).

- 7. **LOAD CONFIG** button: By clicking this button, a configuration file can be loaded into the software. When this is done, all settings from the 'register settings area' are overwritten with the information from the configuration file. The new settings are automatically transferred to FPGA and sensor (no need to click the

- 'reload FPGA button' after loading a configuration file). (Tip: it is allowed to load a configuration file while in video mode. The new settings will reflect in the images immediately.)

- 8. **IMAGE MODE** setting: With this drop-down list, the image mode can be changed.

- 9. **ERROR MESSAGE**: If an error occurs during image grabbing, it is reported in this error message window. If an error message occurs, check if the camera link cables are plugged correctly and if the sensor is plugged correctly. These are the most common sources of frame grabbing errors.

Note: On the Desktop of the evaluation PC, there is an example of a good configuration file. This file has been saved using the 'save config button'. You can load this configuration file into the software with the 'load config button'. This configuration file contains the advised values for optimal sensor operation.

#### 4.3.2 REGISTER SETTINGS AREA

#### 4.3.2.1 SENSOR REGISTERS

| NAME                     | VALUE    | MIN            | MAX         | A | DDRE | SS | SIZE |

|--------------------------|----------|----------------|-------------|---|------|----|------|

| # of frames              | 1        | 1              | 65535       | 2 | 70   | 0  | 16   |

| monochrome               | 1        | 0              | 1           | 2 | 39   | 0  | 1    |

| dual integration         | 0        | 0              | 1           | 2 | 41   | 1  | 1    |

| external integration     | 0        | 0              | 1           | 2 | 41   | 0  | 1    |

| fot length               | 20       | 1              | 255         | 2 | 73   | 0  | 8    |

| integration time (even)  | 50       | 1              | 16777215    | 2 | 42   | 0  | 24   |

| # of slopes (even)       | 1        | 1              | 3           | 2 | 54   | 0  | 2    |

| knee point 1 (even)      | 1        | 1              | 16777215    | 2 | 48   | 0  | 24   |

| knee point 2 (even)      | 1        | 1              | 16777215    | 2 | 51   | 0  | 24   |

| bracketing length (even) | 1        | 1              | 255         | 2 | 55   | 0  | 8    |

| integration step (even)  | 0        | 0              | 16777215    | 2 | 45   | 0  | 24   |

| integration time (odd)   | 2        | 1              | 16777215    | 2 | 56   | 0  | 24   |

| # of slopes (odd)        | 1        | 1              | 3           | 2 | 68   | 0  | 2    |

| knee point 1 (odd)       | 1        | 1              | 16777215    | 2 | 62   | 0  | 24   |

| knee point 2 (odd)       | 1        | 1              | 16777215    | 2 | 65   | 0  | 24   |

| bracketing length (odd)  | 1        | 1              | 255         | 2 | 69   | 0  | 8    |

| integration step (odd)   | 0        | 0              | 16777215    | 2 | 59   | 0  | 24   |

| reg_inte_sync            | 0        | 0              | 1           | 2 | 41   | 2  | 1    |

| reg_dummy                | 0        | 0              | 255         | 2 | 118  | 0  | 8    |

|                          |          |                |             |   |      |    |      |

| Integration              | Windowir | ng             | Signal Path |   |      | 0  | ther |

| FPGA Registers Voltage   |          | and the second | Current     |   |      |    | LL   |

The 'register settings area' can be used to change all sensor registers. All registers in the sensor can be changed or readout from here. The registers are split up over a number of groups, of which the 'integration' and the 'windowing' group are used most often. The other registers contain settings for fine tuning of the analog behavior of the sensor. Most of these settings can be left unchanged by the user of the evaluation system.

Every register setting in this list refers to a sensor register (see data sheet for complete register map). The user of the evaluation system can only change the 'value' of the registers. The other entries are informational. (Tip: the register addresses (third column from the right) match the address values in the register map in the datasheet).

Upon hitting the enter key after changing a value of a register, it is uploaded to the FPGA. Note that it is allowed to change register settings while in video mode. The changes will reflect immediately in the displayed images.

#### 4.3.2.2 FPGA REGISTERS

The registers in this tab control the FPGA for external exposure mode (EXT EXP). The pulses for this mode (T\_EXP1/2 and Frame\_REQ) are generated by the FPGA and cannot be controlled manually by connecting an external signal to the T\_EXP and Frame\_REQ inputs).

The other registers are of no use and should be left unchanged.

| NAME                      | VALUE     | MIN | MAX         | AD | DRES | s s | SIZE |

|---------------------------|-----------|-----|-------------|----|------|-----|------|

| (LS) enable mode (1=sync) | 0         | 0   | 1           | 3  | 15   | 7   | 1    |

| (LS) Red                  | 0         | 0   | 65535       | 3  | 0    | 0   | 16   |

| (LS) Green                | 0         | 0   | 65535       | 3  | 2    | 0   | 16   |

| (LS) Blue                 | 0         | 0   | 65535       | 3  | 4    | 0   | 16   |

| (LS) White                | 0         | 0   | 65535       | 3  | 6    | 0   | 16   |

| show training             | 1         | 0   | 1           | 1  | 3    | 0   | 1    |

| (CL test) test image      | 0         | 0   | 1           | 1  | 2    | 0   | 1    |

| (CL test) chan value 0    | 0         | 0   | 4096        | 1  | 4    | 0   | 12   |

| (CL test) chan value 1    | 0         | 0   | 4096        | 1  | 6    | 0   | 12   |

| (CL test) chan value 2    | 0         | 0   | 4096        | 1  | 8    | 0   | 12   |

| (CL test) chan value 3    | 0         | 0   | 4096        | 1  | 10   | 0   | 12   |

| (EXT EXP) inte tim even   | 0         | 0   | 16777215    | 1  | 15   | 0   | 24   |

| (EXT EXP) inte tim odd    | 0         | 0   | 16777215    | 0  | 6    | 0   | 24   |

| (EXT EXP) knee 1 even     | 0         | 0   | 16777215    | 0  | 11   | 0   | 24   |

| (EXT EXP) knee 2 even     | 0         | 0   | 16777215    | 0  | 14   | 0   | 24   |

| (EXT EXP) knee 1 odd      | 0         | 0   | 16777215    | 0  | 17   | 0   | 24   |

| (EXT EXP) knee 2 odd      | 0         | 0   | 16777215    | 0  | 20   | 0   | 24   |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

|                           | 0         | 0   | 0           | 0  | 0    | 0   | 0    |

| PGA Registers             | Voltage   |     | Current     | T  |      | PL  | L    |

| Integration               | Windowing | ,   | Signal Path | 7  |      | Oth |      |

#### 4.3.3 IMAGE AREA

The images that are acquired from the sensor are displayed in the 'image area'. Only one image is displayed. If a sequence of frames is acquired, the entire burst is in the memory. A selection switch in the 'image statistics area' can be used to select which frame from the sequence is displayed.

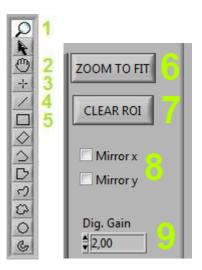

Next to the image plane is a small toolbar with image controls. These can be used to zoom in the image and to select region of interest (ROI) contours for the image statistics. Next figure shows this toolbar.

Of these tools, the following 5 are most commonly used:

- 1. **ZOOM**: When selected, the mouse pointer turns into a magnifying glass when moved over the image. Every click will zoom into the image by 1X. When holding the SHIFT key on the keyboard, the mouse pointer will turn into a magnifying glass with a small 'minus sign' in it. Clicking in the image with the SHIFT key held will zoom the image out by 1X.

- 2. **PAN**: When the image is zoomed, this function allows the user to pan the image.

- 3. **POINT ROI**: Allows the user to set an ROI in the image of exactly 1 pixel. Click on the image to place the point ROI.

- 4. **LINE ROI**: Allows the user to set a line ROI in the image. Click on the image to set the first point of the line. Hold the left mouse key and drag to where the end point of the line should be. Release the left mouse button to place the line.

- 5. **RECTANGLE ROI**: Allows the user to set a rectangular ROI in the image. Click on the image to set the first corner of the rectangle. Hold the left mouse key and drag to the point where the opposite corner of the rectangle should come. Release the left mouse button to place the rectangle.

- 6. **ZOOM TO FIT**: This will reset the zoom level so the image fits the image area.

- 7. CLEAR ROI: This will delete the selected ROI so the whole image will be the ROI

- 8. **MIRROR**: Sets mirroring in X and Y. This is done on the display only. This is not the sensors register settings for flipping. These actions will not be saved to your files.

- 9. **DIG GAIN**: This will multiply your image data (from 0.0 to ...). This is not done with the sensors registers. This action will not be saved to your files and is thus only for viewing the image.

More information on the ROI statistics can be found in the 'image statistics area' section.

#### 4.3.4 IMAGE STATISTICS AREA

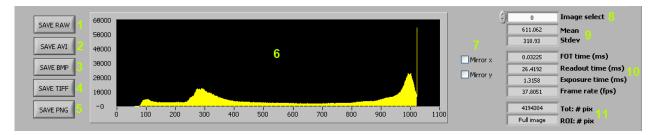

Next figure shows the image statistics area.

The 'image statistics area' consists of:

- **1. SAVE RAW** button: Clicking this button will save the requested images in a raw file format. Set the path and name and the software will automatically add the frame number per image.

- 2. **SAVE AVI** button: If a sequence of images is acquired, the entire sequence can be saved as a movie with the avi format. Click the button and select the path and file name for the movie (including the .avi extension). The playback framerate (fps) of the avi can be changed with the fps selection box.

- 3. **SAVE BMP** button: Click this button to save the images that are in memory as bitmap files. For every image of the sequence that is in memory, two bitmaps will be saved. One with the highest 8 bits of the 10-bit image (called \_msb.bmp). and one with the lowest 8 bits of the same 10-bit image (called \_lsb.bmp). To save the bitmaps, click on the 'save bmp button', navigate to the correct path and enter a name for the images (without the .bmp extension). The software will add the frame number, lsb or msb indicator and .bmp extension to the name that has been entered for every bitmap that will be saved.

- SAVE TIFF button: Clicking this button will save the images in a lossless TIFF file format. Because the images

are 10/12bit most viewers cannot open them directly. ImageJ (<a href="http://rsbweb.nih.gov/ij/">http://rsbweb.nih.gov/ij/</a>) can open our TIFF

files.

- 5. **SAVE PNG** button: Clicking it will save the images in a lossless PNG file format.

- 6. **HISTOGRAM**: Shows the 10-bit histogram of the image that is displayed in the 'image area'. (Note: see next section for explanation of ROI image statistics)

- 7. IMAGE SELECTION control: If a sequence of more than one image is grabbed from the sensor, this control is used to select which of the images is displayed in the 'image area'. The index number '0' identifies the first image of the sequence. If the selection index is larger than the number of frames-1, the 'image area' shows no image.

- 8. **AVERAGE and STANDARD DEVIATION**: Show the average and standard deviation of the selected image in 10-bit values. (Note: see next section for explanation of ROI image statistics)

- 9. **FOT, READOUT, EXPOSURE TIME and FRAME RATE** shows the actual times in ms, calculated from the register values and also the frame rate in fps.

- 10. **PIXEL COUNT** statistics: Show the total number of pixels in the image that is displayed in the 'image area' and the amount of pixels in the selected statistics ROI. (Note: see next section for explanation of ROI image statistics).

#### 4.3.4.1 IMAGE STATISTICS IN ROI MODE

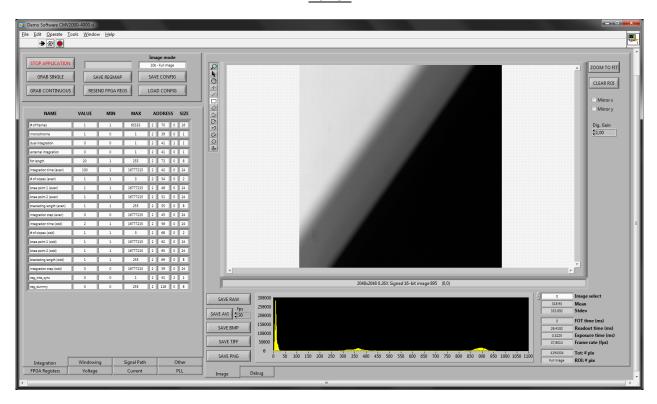

By default, the image statistics apply to the entire image. If statistics of certain areas in the image are desired, the ROI functionality can be used. If an ROI is placed on the image, all statistics that are displayed (histogram, average and standard deviation) are of all pixels that are defined by the ROI.

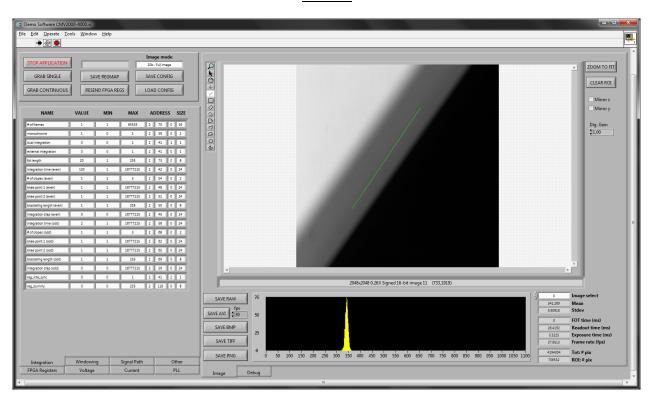

Next figures show examples of the ROI results for different ROIs on the same image. In the examples, note histogram, the average and standard deviation values and the 'ROI # pix' value.

#### No ROI:

#### **Rectangle ROI:**

#### Line ROI:

#### 4.3.5 DEBUG TAB

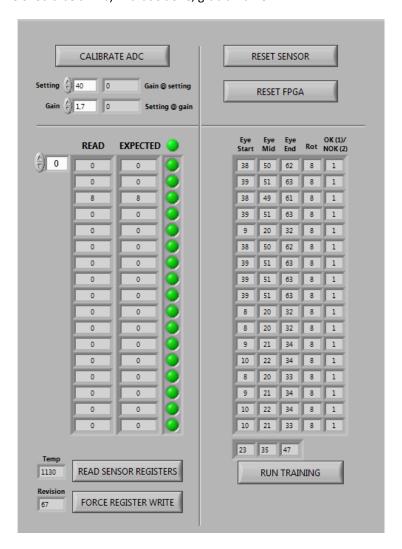

The Debug tab can be used for debugging the sensor.

You can force to write the sensor register values or read them back. If there are differences between the read out value and the value in the software register, the light will turn red.

You can calibrate the ADC gain. Fill in either a ADC register setting to see the actual gain value or vice versa.

You can reset the FPGA or the sensor (default register settings). This is mostly used when you are seeing stability issues or training issues.

Run training will force to do the LVDS output training. If this fails, then probably some register settings are incorrect (PLL, ...). Try resetting the sensor and FPGA or load a good configuration file.

If the sensor keeps failing try stopping the software, closing the application. Then power off the supplies and turn them back on. Wait for the FPGA LED to light up (this means the firmware has been correctly loaded in to the FPGA). And run the executable again. Load a good config file, click on FORCE REGISTER WRITE, then FORCE REGISTER READ, to see if the sensors registers are correctly written. Then run the training a few times (the 4<sup>th</sup> column ROT should be 0 for all channels and column 5 should be all 1's). If that's done, grab a frame.