## Product Document

# AS3701B-BWLM-03

OTP specification for AS3701B-BWLM-03

## **Content Guide**

| 1     | General Description                                      | 3  |

|-------|----------------------------------------------------------|----|

| 2     | Detailed Description of the OTP registers functionality  | 3  |

| 2.1   | General Register Block Description                       | 3  |

| 2.1.1 | I2C Register                                             | 3  |

| 2.1.2 | OTP Registers                                            | 4  |

| 2.1.3 | OTP Fuses                                                | 4  |

| 2.2   | Startup from scratch                                     | 4  |

| 2.3   | Startup during normal operation                          | 4  |

| 3     | Detailed Explanation of the AS3701B-BWLM-03 OTP settings | 5  |

| 3.1   | Timeslots                                                | 5  |

| 3.2   | Delay Interval                                           | 6  |

| 3.3   | Reset Time                                               | 6  |

| 3.4   | Reset Voltage Rise                                       | 6  |

| 3.5   | ON key                                                   | 6  |

| 3.6   | Auto-off                                                 | 6  |

| 3.7   | NTC-Input                                                | 6  |

| 3.8   | USB Current Limit                                        | 6  |

| 3.9   | Supply Reset Enable & Power Off at VSUP-low              | 6  |

| 5     | OTP Fuse Register Setting for AS3701B-BWLM-03            | 8  |

| 6     | Ordering & Contact Information                           | 9  |

| 7     | Copyrights & Disclaimer                                  | 10 |

| 8     | Revision Information                                     | 11 |

## 1 General Description

This Application Note describes the OTP settings of the AS3701B-BWLM-03 variant.

The AS3701B has a One Time Programmable (OTP) Boot ROM, which is factory pre-programmed at final test and leads to a defined default startup behavior of AS3701B.

## 2 Detailed Description of the OTP registers functionality

## 2.1 General Register Block Description

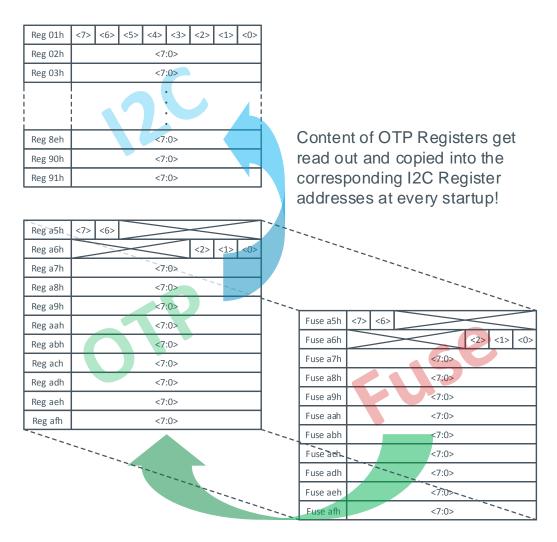

Figure 1: Overview of the OTP registers functionality

Content of Fuses is getting copied into corresponding OTP Register addresses at every startup from scratch!

## 2.1.1 I2C Register

- Accessible via I2C every time (READ/WRITE)

- Content get lost when the system power (VSUP) fails

- Reset to their default state, when a reset command gets initiated

## 2.1.2 OTP Registers

- Only READ via I2C possible

- Entering testmode is mandatory to WRITE onto this registers

- Trimming of chip and setting of dedicated startup sequence

- · Bit setting information comes from Fuse block

- Content get lost when the system power (VSUP) fails

## 2.1.3 OTP Fuses

- Contain all trimming and startup sequence settings

- OTP fuse burning routine:

- Entering Testmode

- WRITE correct bit setting into OTP Registers

- o BURN this information to the corresponding OTP fuses

- Programmed fuses will never lose their information

- Bit setting is getting copied anytime into OTP registers, when a startup from scratch occurs (POR level)

## 2.2 Startup from scratch

Whenever AS3701B has a startup from scratch (first battery insertion or charger adapter insertion without battery) and VSUP increases the POR voltage, the content of the ROM fuses will get read out and copied directly into the corresponding OTP register addresses (see the green arrow)! If the VSUP voltage further increases and reaches the Reset Voltage Rise level, the content of the OTP registers will get read out and copied directly into the corresponding register addresses (see the blue arrow)!

## 2.3 Startup during normal operation

During normal operation, a startup will be initiated whenever the AS3701B gets

- a reset command or

- a wake-up command from stand-by mode or

- a wake-up command from power-off mode

A startup during normal operation implies, that the AS3701B is always supplied via a battery or a charger adapter and the VSUP is always higher than the Reset Voltage Rise level. In this case, at every startup only the content of the OTP registers will be copied into the corresponding register addresses.

If the VSUP level would fall below the POR level, all registers (I2C & OTP registers) will loose their content and consequently the following startup would be from scratch containing the OTP settings stored in the fuses!

ams Application Note Page 4

[v1-01] 2016-Jun-27 Document Feedback

## 3 Detailed Explanation of the AS3701B-BWLM-03 OTP settings

In this chapter, each OTP setting of the AS3701B-BWLM-03 variant will be explained in detail.

## 3.1 Timeslots

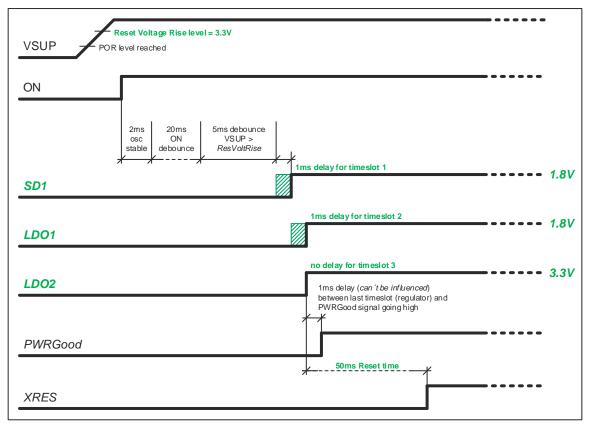

The following diagram should illustrate the startup behavior of the regulators, which are part of the OTP setting!

All the green marked parameters are OTP defined settings!

Figure 2: Startup digram for AS3701B-BWLM-03

For the AS3701B-BWLM-03 variant, there're just 3 timeslots used.

- Timeslot 1 contains the configuration of SD1. The output voltage of SD1 is set to 1.8V and the switching frequency is set to 1MHz! Timeslot 1 starts with a delay of 1ms!

The configuration of timeslot 1 with SD1 is done with the bits <3:0> of fuse register aah.

The parameter settings of SD1 is done with the bits <7:0> of fuse register abh.

- Timeslot 2 contains the configuration of LDO1. The output voltage of LDO1 is set to 1.8V, the output current limit is set to the 200mA range and it's already enabled right after startup! Timeslot 2 starts with a delay of 1ms to Timeslot 1!

The configuration of timeslot 2 with LDO1 is done with the bits <7:4> of fuse register aah. The parameter settings of LDO1 is done with the bits <7:0> of fuse register ach.

- Timeslot 3 contains the configuration of LDO2. The output voltage of LDO2 is set to 3.3V, the output current limit is set to the 200mA range and it's already enabled right after startup! Timeslot 3 starts simultaneously to Timeslot 2!

The configuration of timeslot 3 with LDO2 is done with the bits <3:0> of fuse register adh. The parameter settings of LDO2 is done with the bits <7:0> of fuse register aeh.

ams Application Note Page 5

[v1-01] 2016-Jun-27 Document Feedback

#### 3.2 **Delay Interval**

The delay interval, which defines the delay of a timeslot referring to it's previous timeslot, has its default setting of 1ms.

The delay interval is defined with the bit <7> of fuse register a5h.

#### 3.3 **Reset Time**

The reset time is the duration after timeslot 3 (LDO2) where the XRES signel is still kept low and is set to 50ms.

The reset time is defined with the bits <5:4> of fuse register a7h.

#### 3.4 **Reset Voltage Rise**

The Reset Voltage Rise level is set to 3.3V, whereby the Reset Voltage Fall level automatically jumps to a default value of 3.1V.

The reset voltage rise is defined with the bits <3:1> of fuse register a8h.

#### 3.5 ON key

The ON key is defined as a push button and is configured as active high! This means the ON-key has to be forced to VSUP shortly to assert the ON-key function.

Furthermore the ON-key longpress is activated and a long press on the ON-key to VSUP for >8s initiates a Reset of AS3701B!

The ON-key configuration is a combined definition of the bits <2:0> of fuse register a6h, the bit <0> of fuse register a8h and the bit <2> of fuse register a9h.

#### 3.6 Auto-off

The Auto-off feature is activated!

This feature allows to force the PMIC directly into the Power-off state right after a power-up from scratch (first battery insertion or charger adapter insertion without battery). In this case, the PMIC will not enter the OTP startup stage!

The auto-off feature is defined with the bit <7> of fuse register a7h.

#### 3.7 **NTC-Input**

For the AS3701B-BWLM-03 variant the NTC-input is defined with the XIRQ NTC pin! This pin must be used to connect the NTC resistor of the battery.

The NTC-input is defined with the bits <1:0> of fuse register a9h.

#### 3.8 **USB Current Limit**

The USB Current Limit of the internal pre-regulator is set to 189mA. Whenever a charger adapter is connected to the VUSB input, the input current into the PMIC is limited to 189mA!

The USB current limit is defined with the bits <7:4> of fuse register a7h.

#### 3.9 Supply Reset Enable & Power Off at VSUP-low

Both bits are activated for the AS3701B-BWLM-03 variant, which forces the AS3701 into the Power OFF mode, when the Reset Voltage Fall level (3.3V) is reached!

ams Application Note Page 6

The Supply Reset Enable feature is defined with the bit <3> of fuse register a9h and the Power OFF at VSUP-low is defined with the bit <1> of fuse register a7h.

## 5 OTP Fuse Register Setting for AS3701B-BWLM-03

Register 0xa5 = 0x40 (01000000b)

Register 0xa6 = 0x02 (00000010b)

Register 0xa7 = 0x92 (10010010b)

Register 0xa8 = 0x28 (00101000b)

Register 0xa9 = 0x3d (00111101b)

Register 0xaa = 0x21 (00100001b)

Register 0xab = 0x50 (01010000b)

Register 0xac = 0xcc (11001100b)

Register 0xad = 0x03 (00000011b)

Register 0xae = 0xea (11101010b)

Register 0xaf = 0x00 (00000000b)

## 6 Ordering & Contact Information

| Ordering Code   | Marking | Quantity | Delivery Form | Package        |

|-----------------|---------|----------|---------------|----------------|

| AS3701B-BWLM-03 | 1V2-03  | 500pcs   | T & R         | 20balls WL-CSP |

Note: ams AG also supplies an evaluation board with a mounted AS3701B that can be altered with a software GUI.

With this software the user can determine the desired OTP setting for its application. Please contact ams for your OTP setting requirements. An alternative to the OTP programming is to start up an external uC and boot up AS3701B via the I2C commands.

## Buy our products or get free samples online at:

www.ams.com/ICdirect

## **Technical Support is available at:**

www.ams.com/Technical-Support

## Provide feedback about this document at:

www.ams.com/Document-Feedback

## For further information and requests, e-mail us at:

ams\_sales@ams.com

## For sales offices, distributors and representatives, please visit:

www.ams.com/contact

## Headquarters

ams AG

Tobelbaderstrasse 30

8141 Premstaetten

Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

## 7 Copyrights & Disclaimer

Copyright ams AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Information in this document is believed to be accurate and reliable. However, ams AG does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Applications that are described herein are for illustrative purposes only. ams AG makes no representation or warranty that such applications will be appropriate for the specified use without further testing or modification. ams AG takes no responsibility for the design, operation and testing of the applications and end-products as well as assistance with the applications or end-product designs when using ams AG products. ams AG is not liable for the suitability and fit of ams AG products in applications and end-products planned.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data or applications described herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

ams AG reserves the right to change information in this document at any time and without notice.

## 8 Revision Information

| Changes from previous version to current revision 1-01 (2016-Jun-27) | Page |

|----------------------------------------------------------------------|------|

| update of figure 2                                                   | 5    |

| Ordering & Contact Information                                       | 9    |

| Copyright & Disclaimer                                               | 10   |

**Note:** Page numbers for the previous version may differ from page numbers in the current revision. Correction of typographical errors is not explicitly mentioned.